Intel Foundry Services’ (IFS) Accelerator program is showing how technology progresses when small and big names join forces in partnerships.

On June 28, 2022, IFS announced a new program called Cloud Alliance as part of its Accelerator program. Cloud Alliance is built to secure design environments in the cloud while streamlining design efficiency for foundry customers using on-demand compute. Some of the first members of Cloud Alliance include cloud providers Amazon Web Services and Microsoft Azure along with big names in electronic design automation (EDA): Ansys, Cadence, Siemens EDA, and Synopsys.

The stated goal of IFS is to become one of the world’s leading foundries.

The IFS Accelerator program was previously built upon three key pillars—EDA Alliance, IP Alliance, and Design Services Alliance—to help small companies and startups access scalable chip manufacturing. Now, with a fourth pillar, Cloud Alliance, small companies have a leg up on on-demand cloud design platforms that would have been too expensive and slow to achieve independently.

Intel Foundry Services’ Accelerator Ecosystem

Because of the chip shortage, fabless chipmakers have limited chip design resources to offer startups. Now, with Cloud Alliance, small companies that have relied on fabless design services can now get direct access to foundry manufacturing. This support includes not only foundry capabilities but also tools to fully incorporate ideas in the design process and cut down time-to-market. Startups can even maximize all the benefits of ASIC design, for example.

IFS Accelerator intends to bring silicon products to market faster through company collaborations. These partnerships pool resources, so small companies can access chip design hardware and software on-demand, including EDA tools, silicon-verified intellectual property, and design services.

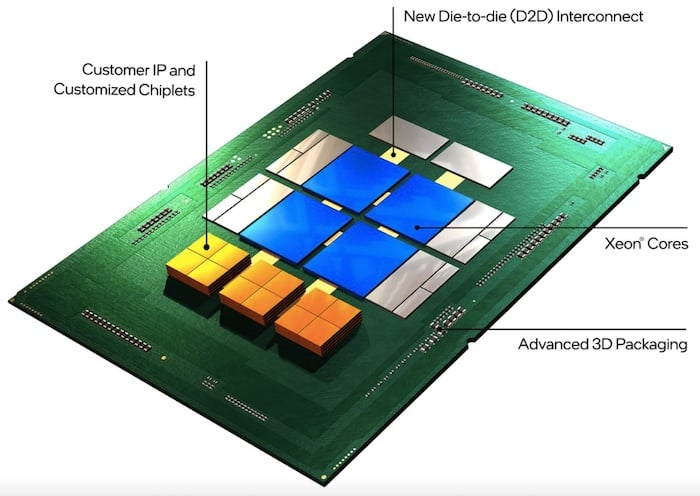

With the popularity of 3D packaging technology, chip architects are increasingly pushed toward modular designs, like “chiplets.”

Such EDA tools help designers model system performance, estimate power needs, reduce chip manufacturing errors, and put logical ideas into computer form. IFS also aims to ease the burden of IP verification engineers, who must test system-on-a-chip (SoC) designs by accessing existing interfaces, memory, and protocol requirements. IFS’ reusable and integrated IP blocks can help shorten time-to-market for new silicon products.

Phase One of IFS Accelerator

Intel rolled out the preliminary phase of Accelerator back in September 2021. The core idea of this program was to provide advanced semiconductor manufacturing technologies to automotive chipmakers who so desperately needed versatile, customized, and industry-standard IP solutions. The openness and freedom of Intel’s IP framework could help these companies practice innovation without risking IP confidentiality.

Phase one was rolled out by 17 partnering companies involved in all three pillars of Accelerator, including:

- EDA Alliance: Cadence, Ansys, Synopsys, Siemens EDA

- IP Alliance: Arm, SiFive, Synopsys, Cadence, Alphawave, Vidatronic, Analog Bits, Andes, eMemory, M31, Silicon Creations

- Design Services Alliance: Wipro, Capgemini, Tech Mahindra

A New Team of Partners: IFS Cloud Alliance

Phase two of IFS Accelerator is to build a modern and powerful foundry ecosystem through IFS Cloud Alliance—a massive on-demand compute system supported by the two largest cloud platforms, AWS and Microsoft Azure, and EDA partners. Using Intel’s process design kits, designers can access generic fabrication methods to reduce costs, shorten the design cycle, optimize layouts, and preserve in-house know-how.

Intel esteems its IFS Alliance as a major step toward releasing the pressure of the chip shortage. Small companies receive on-demand access to Intel’s manufacturing capabilities, including processing and packaging, and a reliable and secure design environment in the cloud. This partnership also bridges the gap between hardware, software, and data—bringing engineers, machines, and processes into a shared space.